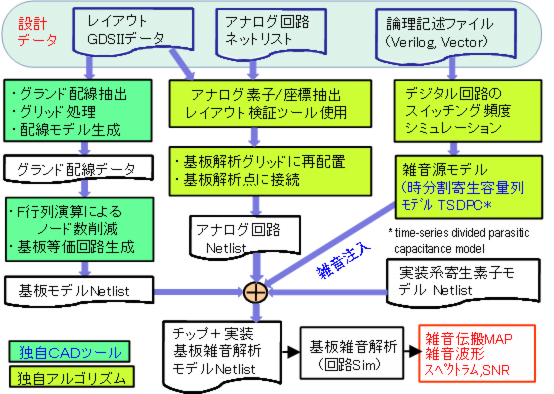

基板雑音解析回路モデル生成・解析フロー

モデル作成・解析手順

- レイアウト情報(GDSII),回路情報(アナログ:SPICEネットリスト,デジタル:Verilog記述)を入力する.

- GDSからグランド配線を抽出し,Si基板の抵抗メッシュに載せてF行列演算でノード数を2桁減少させる.

- 論理シミュレーションにより,デジタル回路の発生する雑音をTSDPCでモデル化する.

- 基板モデル,アナログ回路,論理回路を統合し,実装回路素子を追加する.

- システムレベルのモデルが完成する.

- 回路シミュレータでAC,TRAN解析をする.

- 雑音波形,雑音伝搬(減衰)マップ,雑音スペクトラムなどを算出する.

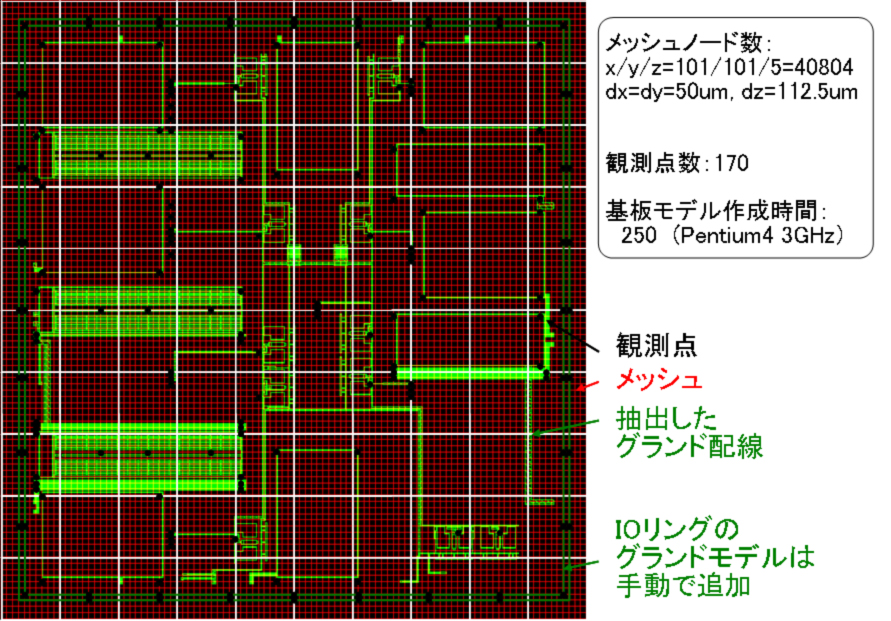

チップレベル雑音解析モデル

モデル化(1)

- 赤線:初期設定メッシュ

- 緑線:抽出したグランド

雑音電圧をシミュレーションする.ノードは観測点として指定して,削減しない.この例では40804ノードを170ノードに削減している.

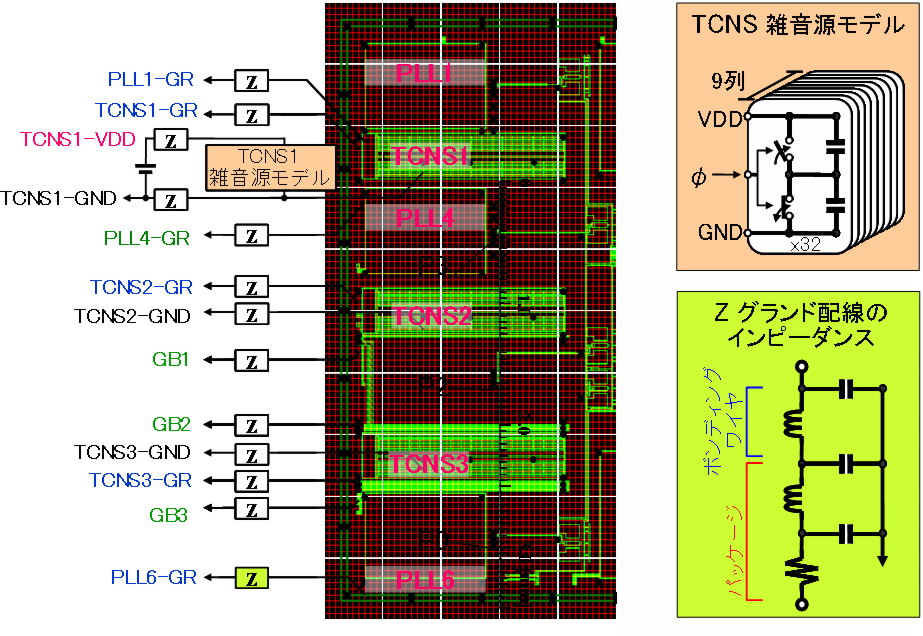

ボードレベル雑音解析モデル

モデル化(2)

CMOS論理回路の寄生容量の充放電を考慮.寄生容量値が動作ベクトルで変わる.配線のインピーダンスとして,パッケージのリード,PCB上のパターン,チップ上のメタル配線を考慮.高周波領域ではインダクタンスが支配的になる.

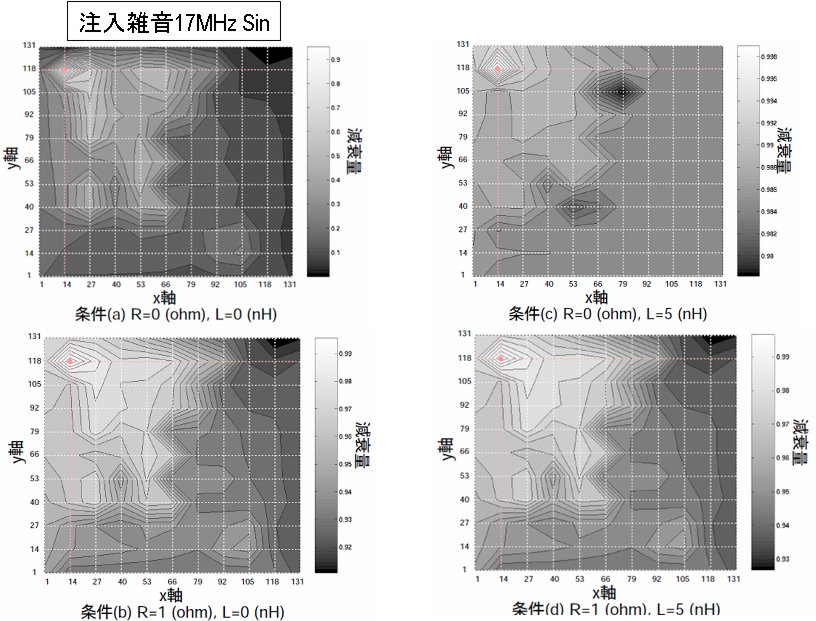

シミュレーション結果(雑音伝播マップ)

雑音伝搬量のチップ表面の分布をあらわす.

- メッシュ状解析点での雑音伝搬量を濃度分布で示す.

- 雑音源は任意の解析点にDC,ACで与える.

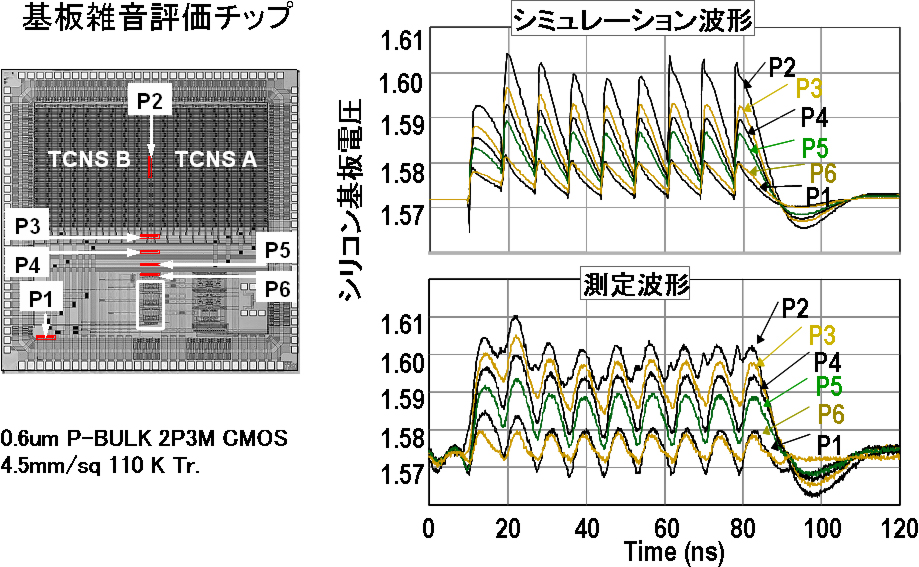

基板雑音測定例

- 左図 :基板雑音テストチップ

- 右上図:シミュレーション波形

- 右下図:測定波形

クロストーク雑音波形の測定値とシミュレーション値とを比較すると,雑音波形の概形および振幅はだいたい合っている.雑音伝搬経路および雑音検出回路の帯域がシミュレーションでは実際より広いため,波形に高周波成分が多くなっている.