## アナデジLSIの雑音解析EDAツール

# A-R-Tec Corp.

http://www.a-r-tec.jp, 082-421-4222

### FPNA (Floor Plan Noise Analysis)

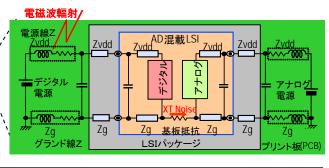

フロアプラン(含む実装系)でアナデジ混載LSIの 基板・グランド雑音を解析できるツール

特徴・ブロックの属性記述ノウハウを組み込んだフロアプラン記述

- •Fマトリクス演算でノード数を(1/100)削減する技術

- ・論理回路の雑音源モデル: 容量充放電モデル(TSDPC)

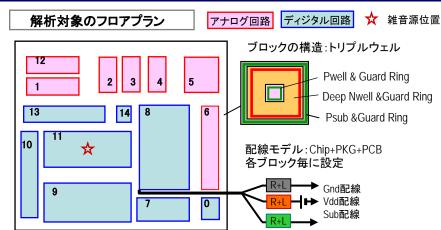

#### 解析可能構造

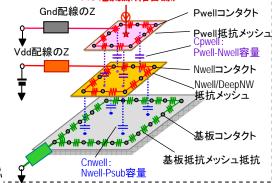

#### 基板構造

- •P基板-Nウエル

- ·N基板-Pウエル

- ・トリプルウエル (P基板-Deep Nウエル-Pウエル)

- ·SOI構造

#### 雑音抑圧構造

- ・ガードバンド

- ・シールド

- ・トレンチ

- ·SOI構造

#### 雑音源情報

- 雑音源プロパティ 論理回路, アナログ回路

- 接続ノード

- ・正弦波/パルス雑音源 解析条件

#### 雑音源モデル生成

論理ファイル(Verilog)

論理レベル電源流Sim

**TDSPC** モデル

簡易等価 回路モデル

#### モデル化のためのフロアプラン情報

#### チップ情報

- ・プロセス

- ・サイズ

- •基板抵抗率

- ・ウエル容量

- •配線抵抗

- ・ メッシュ数 (X/Y/Z)

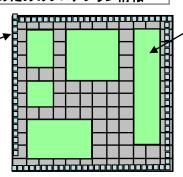

#### ブロック情報

ウェル構造 (トリプルウエル?) BLKサイズ, 位置座標 (x1,y1) (x2,y2)

#### BLK内配線

- •幅,配線層

- •Row数 / Column数

#### BLK間配線

- ・幅・配線層・長さ

- ·BLK内接続座標

- •接続先情報

- 共通接続ノード

P基板

### FPNA処理フロー

#### フロアプラン入力GUI

フロアプランデータ入力 フロアプラン表示 データチェック

#### 基板モデル生成

容量. 配線 モデル生成

- ウエル容量

- •Pad間容量

Si基板モデル化

- シート抵抗

- •Block間 L.R

# Psub, Pwell

- コンタクト抵抗

#### 解析モデル圧縮

観測点. 接続点設定 F行列演算による 基板等価回路生成

### 基板モデル Vdd配線—▶ N Well Gnd/Sub配線

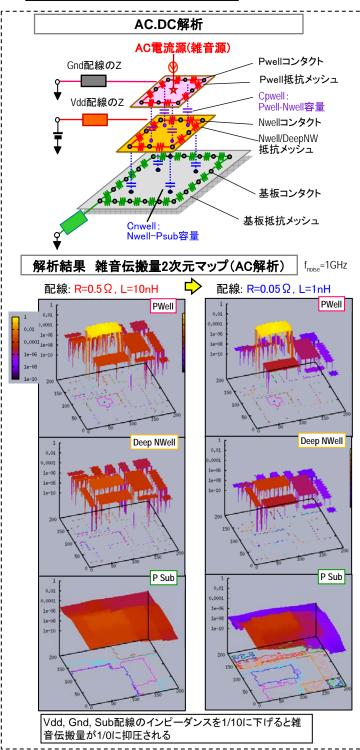

### AC電流源(雑音源)

実装系モデル生成 パッケージ、基板の 寄生素子モデル

システムレベル解析モデル合成

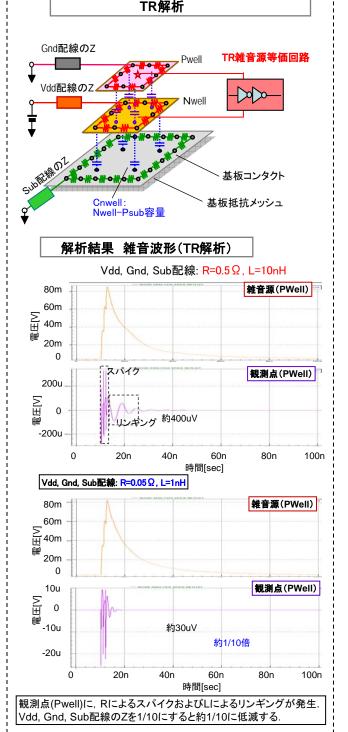

#### 回路シミュレーション (SPICE)

DC解析

AC解析

TR解析

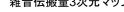

#### 解析結果 雑音伝搬量2次元マップ

-80

-100

-140

クロストーク雑音波形

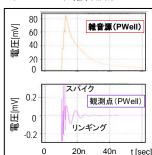

#### 雑音伝搬量周波数特性

雜音源 (Psub)

雑音伝搬量3次元マップ

音伝搬量

# FPNAデモンストレーション

# A-R-Tec Corp.

http://www.a-r-tec.jp, 082-421-4222

#### 解析条件

- ・基板のメッシュ数:。\_\_...

- x:200, y:200, z(チップ厚さ方向):2

- •観測点:20x20

- ・実装系モデル: Vdd, Gnd, Sub配線のR,L (QFP+PCB, CSP+PCBも可)