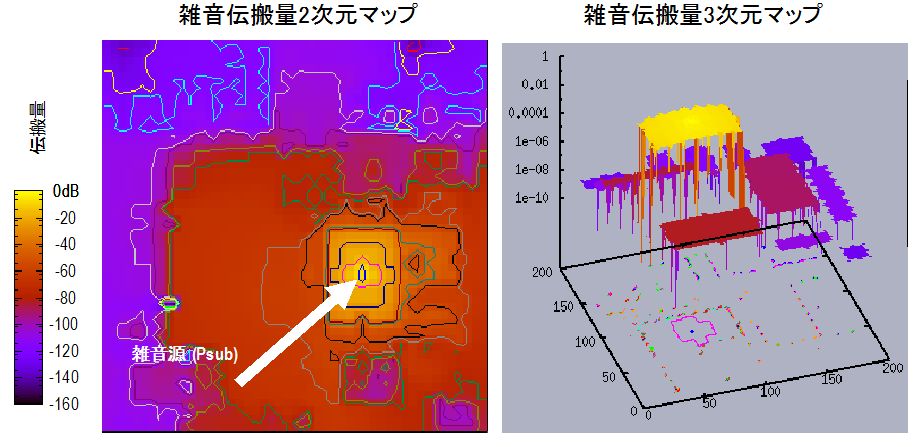

アナデジ混載LSIの設計において,CMOSロジックの動作時に生じる過渡的電流変化と,それが基板伝播して起こる基板クロストーク雑音を如何に解決するかが重要な課題となっております.弊社ではこれを解決してシグナルインテグリティを達成するための技術として,設計の初期段階で基板雑音に強いフロアプランを実現するための強力なツール(Floor Plan Noise Analysis:FPNA)を販売しております.

FPNAによるクロストーク雑音の定量的な評価により,リワーク回数と経費を削減でき,高性能なアナデジ混載LSIの最適設計や設計効率の向上が可能になります.特にRF回路,アナログ回路を,高速大規模ロジックと混載した非常に広い周波数範囲とダイナミックレンジを要求されるLSIの開発には,不可欠なキー技術です.雑音解析技術は,解析ツール販売・サポート,解析請負,技術指導,解析環境構築,新規技術開発など,ご要望に応じて種々の形態で提供致します.

フロアプランレベルではなく,GDSデータを元にした解析(GDSNA)も弊社の技術で対応可能ですので,ご相談ください.

FPNAの特長

- 詳細なレイアウト設計の前に,フロアプランレベルでクロストーク雑音の影響を見積もることが可能.

- GDSデータは不要で,基板抵抗率やガードリング等の必要最小限の情報に基づいて短時間で計算が可能.

- 複数のフロアプラン候補に対して,本ツールを適用することにより,最適な案を短時間に選択決定することが可能.

FPNA関連資料

- FPNA ver. 1.0 のカタログ

- FPNA ver. 1.0 の特徴,GDSベース解析と比較

- FPNA ver. 1.0デモ @EDS Fair 2010

- FPNA ver. 1.0 の解析例

- ASP-DAC 2006の発表スライド

- 日経テクノロジー・オンラインの記事

FPNAに必要な情報

FPNAを実施するために必要となる情報は以下になります.

プロセス情報

- 基板種類(N型基板,P型基板)

- ウェル構造(ツインウェル,トリプルウェル)

- 基板抵抗率 [Ω・cm]

- コンタクト,ビア抵抗 [Ω/個]

- コンタクト,ビアサイズ [um角]

- ウェルのシート抵抗 [Ω/□]

- ウェル-基板間容量 [fF/um2]

- ウェル-ウェル間容量 [fF/um2]

- 配線のシート抵抗 [Ω/□]

チップサイズ

- x方向 [um]

- y方向 [um]

- z方向(チップ厚) [um]

フロアプラン情報

- フロアプラン図

- 電源,グランドの配線パターン情報(ガードリングを含む)

- 電源,グランドのパッド配置情報

- オンチップのパスコン情報(値,位置)

- ESD保護素子の情報(容量値)

ある程度正確な座標情報が必要となります.既にGDSデータがある場合は上記情報を抽出可能です.

パッケージ,評価基板情報

- パッケージ種類(QFP,QFN,CSP,・・・)

- ボンディングワイヤ長 [mm]

- 評価基板上のパスコン情報(値) [nF]