# A-R-Tec Analog and RF Technologies

株式会社エイアールテック

URL: http://www.a-r-tec.jp Email: info@a-r-tec.jp

会社の役割:アナログ回路とRF回路に関する「設計・評価技術の開発」と「人材育成」を 両輪として実施し、日本の全産業と先端科学技術の発展に貢献すること...

# ビジネスの三本柱

# アナログ回路の設計

MADC MILL

高精度・低電力などの高度な要求仕様に応じて、基本マクロをベースにカスタム設計.

# 提供するアナログ回路

- ·AD変換器

- ·DA変換器

- 低雑音アンプ

- ・アナログフィルタ

- CMOSイメージセンサ

- ・センサーインタフェース

- ·VCO, MIX, PLL

- インダクタ結合回路

#### 業務形態

- ・アナログIPの設計・開発

- ・IP搭載LSIの設計・開発

- ・アナログ測定技術

- ・LSI開発コンサルティング

# 基板 電源雜音解析

1001011 1011100 0010011

アナ・デジ混載LSIで課題となる、Si基板や電源を通したクロストーク雑音(XT)を解析、評価、抑圧する技術を提供、

# 基板/電源雑音の独自技術

- ・雑音解析モデル化技術

- ・雑音シミュレーション技術

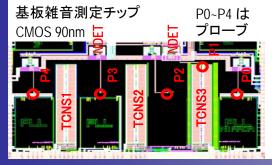

- ・雑音テストチップ設計技術

- ・オンチップ雑音測定技術

- ・雑音耐性の高い設計技術

# 業務形態

- ・解析ツール販売, サポート

- ・雑音解析モデル作成

- ・雑音シミュレーション

- ·基板雑音評価/TEG設計

- ・オンチップ雑音測定

- 雑音対策コンサルティング

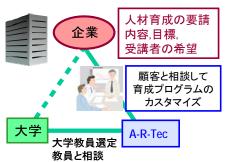

# アナログ設計者のOJT

アナログ・RF回路では多種の特性を考慮した設計が要求され、CAD自動設計は無理. 設計の経験とノウハウが必須. オンザジョブ育成(OJT)により実践的アナログ設計者を育成.

受講者の経験と設計目標と する回路と性能に応じて.

- ・カリキュラムをカスタマイズ、

- ・基礎から実践力まで育成.

- •回路の設計資産も獲得.

OJTへの導入のため基礎実践講 座(大学で実施)も提供.

- •CADを用いたAD変換器設計

- •OPA,ADCの全項目を測定

- ・カタログを理解する力を習得

# ご挨拶

高度情報社会の基盤となるエレクトロニクスではプロセッサ・メモリ・アナログ・無線・センサを集積化し、 高性能と省エネルギーを両立させる必要があります. システムの小型化, 低電力のために, これらを

1チップ化することが有効ですが、アナログ回路の設計はデジタル回路の様なCAD化が進んでおらず、経験を持った技術者の数も不足しています。

又, 人間の健康と安全のために, 脈拍や血糖値などの生体情報を常時監視するモニタ, 脳波や神経信号を検出・制御するシステムなどの開発が進んでいます. センサとのインタフェースとして, アンプやAD変換器などのアナログ回路が必須であり, その高感度化, 低電力化が重要となっています.

このような要請に応えるべく、2001年4月に大学の研究成果をもとにして、先端アナログ回路設計・開発を業務とする (株)エイアールテックを設立しました。10年間に渡り、高度なAD変換器などのアナログ回路設計の業務、クロストーク雑音解析と雑音抑圧設計の業務、実践的なアナログ設計者の育成などを事業化して、半導体産業に貢献して参りました。又、大学や研究機関における物理学、医科学、天文学の研究用の新機能、高性能チップの開発も拡大し、先端科学技術にも貢献できるようになりました。

今後とも、大学と連携して新技術開発とその実用化に積極的に取り組み、大学と産業との架け橋の役割も果たして参りますので、エイアールテックをご愛顧いただきますようお願いいたします.

アナログ・デジタル混載LSIにおいて、ロジックの動 作時に生じる過渡的電流変化によって起こる電源 雑音および基板雑音がクロストーク雑音としてアナ ログ回路性能を劣化させるので、その抑圧が重要 な課題となっています.

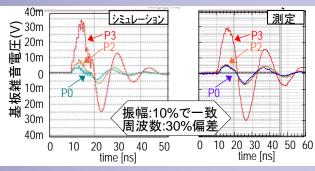

このために、オンチップの雑音検出器による電源および 基板の雑音の測定技術、Si基板と実装ボードを含めた雑音解 析モデル(雑音発生モデル、伝搬モデル)、チップ規模の高速 かつ高精度なシミュレーション技術を保有しています. 設計段 階で雑音を定量的に評価することにより、アナデジ混載LSIの 最適設計ができ、リワーク回数を減らして効率化が図れます.

これらの技術を解析の請負、解析ツールの販売サポート. 解析環境構築,技術開発など,種々の形態で提供します。

#### クロストーク雑音 ∃اہ 論理から 基板への 雑音注入 Si基板抵抗メッシ 電磁波輻射 雷源線Z AD混載LSI Zvdd / / Zvdd Zvdd Zvdd アナログ デジタル アナログ 雷源 電源 ത്ത Zg Zg 基板抵抗 Zg Zg グランド線Z LSIパッケージ プリント板(PCB)

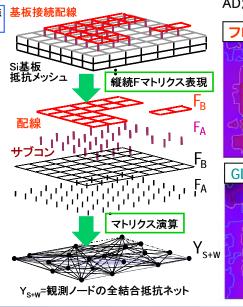

# 雑音解析技術とツール

電源雑音解析を実現する 基板モデル. 論理回路

雑音源モデルを開発

- ・独自Fマトリクス演算で ノード数削減 (1/100)

- ・容量充放電モデルで 論理回路雑音生成

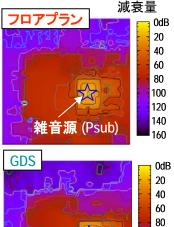

# **FPNA**

Floor Plan Noise Analysis 詳細レイアウト設計前に フロアプランで評価可能 短時間モデル生成可能

# **GDSNA**

**GDS** based Noise Analysis チップ製造前にレイアウト データからで雑音解析, SNRなどの性能を予測

#### 雑音源/観測点 フロアプランデータ 解析条件指定 ・ブロック配置 ブロック属性 入力データ取り込み ン配置 データチェック Si基板モデル化 容量. 配線 Psub, Pwellシート抵抗 モデル生成 コンタクト面積,抵抗 ウエル容量 Pad間容量 •Block間 L.R F行列演算による ·実装 L.R 基板等価回路生成

FPNA処理フロー

雑音源/観測 点モデル化 システムレベル解析モデル 回路Simソースファイル作成 基板雑音シミュレーション

(Hspice/Spectre)

# 抵抗メッシュとFマトリクス演算

基板雑音伝搬マップ AD混載 5x5mmCMOS

100

120

140

160

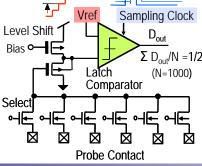

# オンチップ雑音測定用マクロ(雑音検出器,雑音源)

#### 高感度, 広帯域の検出器

等価サンプルの原理で繰り返し クロストーク雑音を計測できる. 高精度 △V=0.1mV, △t=100ps 繰返波形用, 測定時間が長い

アナログ検出器 長時間での発生頻度を検出. 中精度 ΔV=1mV, Δt=1ns

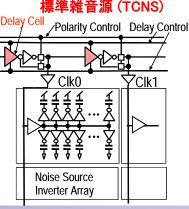

# 遷移制御雑音源(TCNS)

CMOS論理のスイッチング 極性と遅延を制御

#### **∠**V=0.1mV $\Delta t = 100p$ Sampling Clock Level Shift 1 Bias •— $\Sigma D_{out}/N = 1/2$ 16 Latch (N=1000)

等価サンプル雑音検出器 (NDET)

# CMOS 0.18um 基本マクロ Clk<sub>in</sub>⊶ 2.5mm□ NDET

雑音源 (Psub)

# 雑音測定用テストチップ開発と雑音測定

雑音測定システム

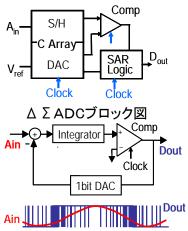

# AD変換の原理と特徴

- ・逐次比較型 1個のDACとCompで1bitずつ順番に比較. 回路規模が小さく超低電力,変換速度は速くないが高分解能.

- ・並列比較型(フラッシュ) 多数の比較器とVrefを用いて並列に比較. 変換は超高速であるが、回路規模が大いので、低分解能・電力大、

- パイプライン型 1~2bitの変換ステージをパイプライン並列動作。 変換はステージの動作で決まるので高速, 高分解能, 低電力.

- ∆ ∑型 オーバサンプルとノイズシェーピングで量子化雑音抑圧.

アナログ回路規模は小、低精度の回路で、超高精度を実現、 各型式の基本マクロをカスタム化して、高性能と省エネを両立、 さらに雑音耐性の高いADCブロックを提供します.

# 逐次比較ADCブロック図 Comp

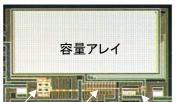

逐次比較ADCチップ写真

S/H スイッチ コンパレータ 2次 Δ Σ ADCチップ写真

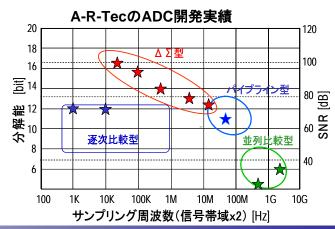

# 各種ADCの性能領域

|         | 分解能<br>(bit) | 帯域(Hz)  | SNR<br>(dB) | Power<br>(mW) |

|---------|--------------|---------|-------------|---------------|

| 逐次比較型   | 8            | 10—10M  | 47dB        | 0.01-0.1      |

|         | 10           | 10−5M   | 60dB        | 0.05-0.5      |

|         | 12           | 10−5M   | 70dB        | 0.1-2         |

| 並列比較型   | 4            | 500M-5G | 24dB        | 0.1-1         |

|         | 6            | 300M-4G | 35dB        | 0.5-5         |

|         | 8            | 200M-2G | 45dB        | 1-10          |

| パイプライン型 | 10           | 1M-100M | 60dB        | 1-3           |

|         | 12           | 1M-100M | 70dB        | 3-5           |

|         | 14           | 1M-20M  | 82dB        | 5–10          |

| ΔΣ型     | 12           | 10-10M  | 70dB        | 0.2-5         |

|         | 14           | 10-1M   | 82dB        | 0.4-10        |

|         | 16           | 10-100K | 94dB        | 0.5-10        |

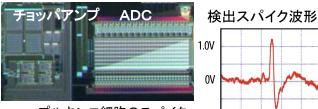

# CMOSアンブ

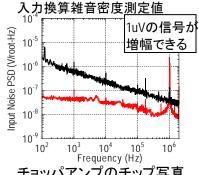

# ローノイズアンプ

MOSトランジスタの1/f雑音と オフセット電圧を抑圧する技術

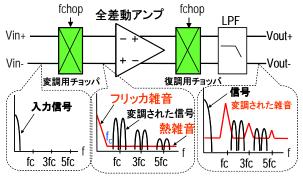

#### チョッパ技術

信号を変調して高い周波数に移動 させ1/f雑音の低い周波数で増幅し て,復調してもとの周波数にもどす.

#### オートゼロ技術 CDS

(Correlated Double Sampling)

信号をサンプルする直前に雑音の みをサンプルし、その状態を基準と して, 信号成分を増幅する. 周期よ り低い雑音成分は除去される.

#### チョッパアンプの基本構成

熱雑音支配となるコーナ周波数 fc

- ・入力を変調し、fcより高周波に変換して増幅

- 復調用チョッパで低周波数に戻す

- fc付近の雑音をLPFで除去

チョッパアンプのチップ写真

L結合インタコネクション

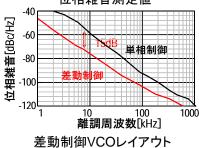

# VCO, PLL

# LC-VCO, Ring-VCO PLL, DLL, クロック発生

周波数帯域:100M-5GHz ジッタ:1-10ns, 電源:1V

差動制御LC-VCO Vout

# 位相雑音測定値

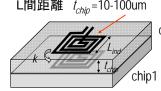

# 3次元集積,非接触テストのデータ転送基盤技術

スパイラルインダクタ対 Lサイズ L<sub>ind</sub>=50-100um **L間距離** *t<sub>chip</sub>*=10-100um

L結合トランシーバ回路 Vdd Vdd chip2 Comp. Vref |

レイアウト (4CH) L<sub>ind</sub>=100um

Bit Rate: 10M - 2G<sub>bps</sub> (1mW/G<sub>bps</sub>)

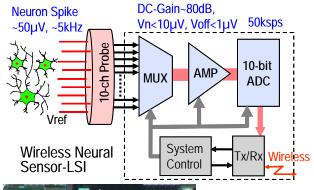

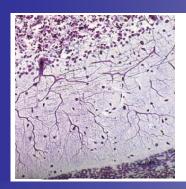

# 神経スパイクセンサチップ

チョッパアンプ、逐次比較ADCを用いて、 10uVの脳波や神経信号を検出し,無線通信.

プルキンエ細胞のスパイク -1.0V 波形が無線で測定できる

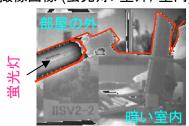

# CMOSイメージセンサ-

光量に対して露光時間とゲイン 適応型方式で浮動小数点データを 出力し、100dBのDレンジを達成

ワイドレンジカメラ

撮像画像(蛍光灯.室外,室内)

# 各種センサー

センサーの性能を引きだす インタフェース回路を開発

容量変化センサー

(圧力, 加速度)

- CV変換アンプ

- •CV変換ADC

電荷センサー

高エネルギー粒子センサ

- 広レンジX線イメージャ

- 高感度X線イメージャ

- オンチップ温度センサー

- •高分解能 0.1℃,

- ·広レンジ 200℃

MEMSインタフェース

# アナログ設計者のオンザジョブトレーニング (OJT)

企業からのアナログ設計者の若手育成の要請は多く、しかも多岐にわたります

- ①電子回路が専門ではないので基確知識から学び、アナログ回路の設計ができるようになりたい。

- ②パイポーラトランジスタを用いたアナログ回路設計の経験を活かしてCMOSアナログ設計の専門家になりたい.

- ③高周波, 低電力, 低雑音など高度なアナログ回路の設計ができるようになりたい.

- ④ニューラルネットなど新しいアナログ回路の構成法や設計技術を身に付けたい.

このような要請に対して、A-R-Tecではセミナーのような受身の教育ではなく、マンツーマンのオンザジョブ育成を提 供しています、OJTのターゲットとスケジュールは個別に相談して決めます。これに基づいて、被育成者が自らの意思 で実践できる環境を提供し、要所で適切な指導を行います. 日常業務から一定期間離れて、集中して能力開発に取 り組むのです、大学で学生とともに学ぶことでリフレッシュできると好評です。

# OJTプログラムの内容

回路機能レベルと技術取得ステップの組合せで構成.

(1). 回路機能レベル(C1-C4)

アナログ設計未経験者はC1~C3までを推奨します。 経験者は、C2から複数選択、C3から一つ選択、

C1. アナログ回路基礎技術

デバイスモデル, カレントミラー バイアス回路ソース接地アンプ, 差動アンプ

C2. アナログ基本回路設計技術 OPA, Comparator, VCO, LNA, Mixer

C3. アナログ機能IP設計技術 PLL, ADC.DAC, アナログフィルタ

C4. アナデジ混載チップ電源·基板雑音評価

# (2). 技術取得ステップ期間(代表例)

S1. 回路基礎知識(C1)

1カ月

S2. 回路シミュレーション(C1, C2. C3)

2カ月

S3. レイアウト設計(C2, C3)

2カ月

S4. 設計検証(C2. C3)

1カ月

マンツーマン指導

# 会社概要

取締役

社名 株式会社エイアールテック 2001年4月3日 設立 資本金 1,000万円 代表取締役社長 岩田 穆

岩田澄子

杉本泰博(中央大学教授) 技術顧問 永田 真(神戸大学教授)

吉田 毅(広島大学助教)

#### 所在地

本社 〒739-0005東広島市西条大坪町10-29-1205 TEL/FAX: 082-422-8378

広島デザインセンター センター長: 岩田 穆 〒739-0046東広島市鏡山3-13-26 広島テクノプラザ405号室 TEL/FAX: 082-421-4222

神戸デザインセンター センター長: 益子耕一郎 〒657-8501神戸市灘区六甲台町1-1 神戸大学自然科学3号館714号室 TEL/FAX: 078-803-6221